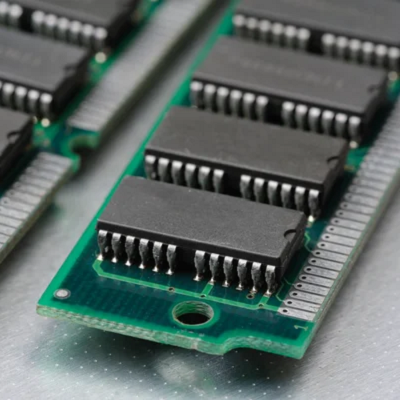

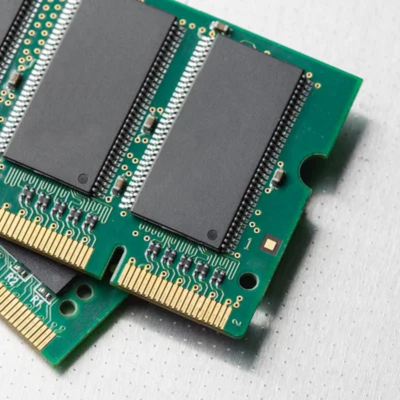

DRAM

Dynamic Random Access Memory (DRAM) stores data in a capacitor. These capacitors leak charge so the information would fades unless the charge is refreshed periodically. Because of this refresh requirement, it is a dynamic memory as opposed to SRAM and other static memory. The advantage of DRAM is its structural simplicity: only one transistor and a capacitor are required per bit, compared to six transistors in SRAM. This allows DRAM to reach very high density.

DRAM is based on a one-transistor, one-capacitor (1T1C) cell structure. The cells are arranged in a rectangular, grid-like array. In simple terms, a voltage is applied to the transistor in the DRAM cell. The voltage is then given a data value. It is then placed on a bit-line. This, in turn, charges the storage capacitor. Each bit of data is then stored in the capacitor. Over time, the charge in the capacitor will leak or discharge when the transistor is turned off. So, the stored data in the capacitor must be refreshed every 64 milliseconds.